Vivado怎么生成HDL例化模板

本篇内容介绍了“Vivado怎么生成HDL例化模板”的有关知识,在实际案例的操作过程中,不少人都会遇到这样的困境,接下来就让小编带领大家学习一下如何处理这些情况吧!希望大家仔细阅读,能够学有所成!

首先要安装

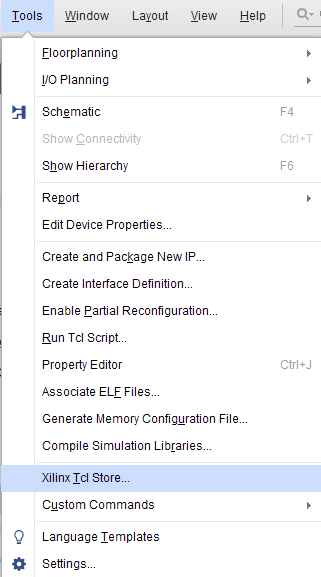

Design Utilities, 点击Tools->Xilinx Tck Store选项,如下图1所示。

图 1.

点击

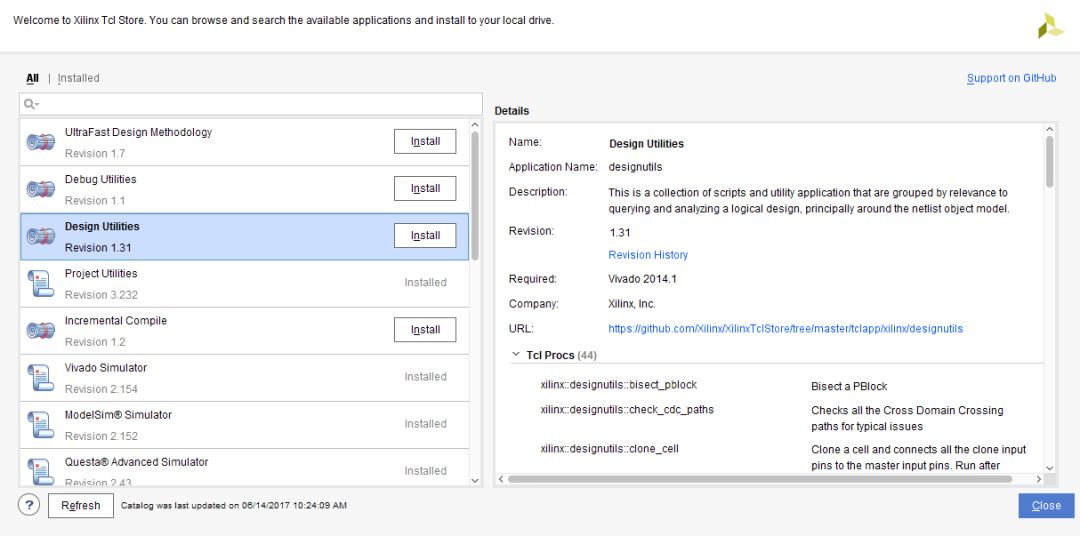

Install, 安装Design Utilities,如下图2所示。

图 2.

之后再生成例化模板时就不需要再安装了,直接进行下面的步骤就行。

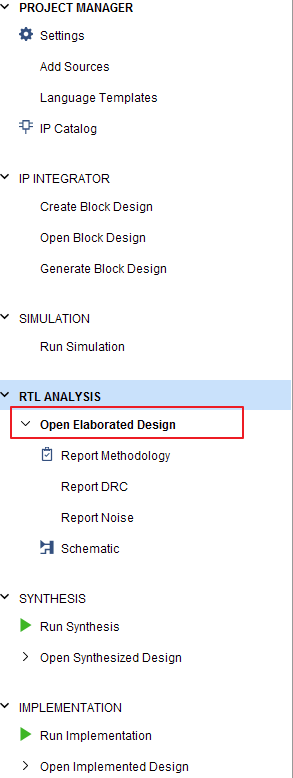

把要生成例化模板的HDL文件设置为top文件,并点击

Open Elaborated Design,如下图3所示。

图 3.

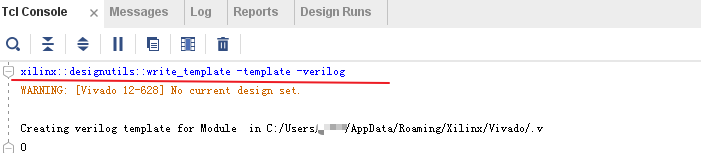

在

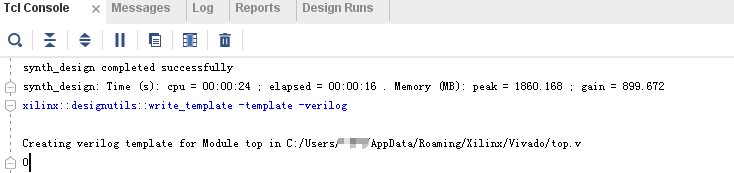

Tcl Console中执行xilinx::designutils::write_template -template -verilog指令,就可以看到下图4所示,根据提示内容,去对应位置找到生成的例化模板文件即可。

图 4.

如果没有执行第3步操作,就会出现下面的情况

图 5.

可以看出,提示了Warning,并且生成了一个没有名字的.v文件。如果打开文件的话,会发现文件中并没有有用内容。

好,到这里,就已经正确生成了HDL例化模板了。但每次都需要输入tcl指令还是略显麻烦,我们可以设置一个tcl的按钮,一键生成。操作如下:

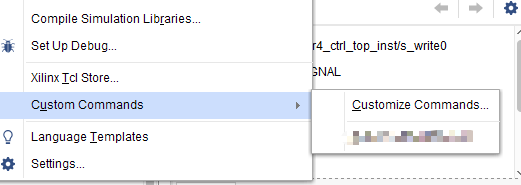

点击Tools->Custom Commands->Customize Commands,如下图6所示。

图 6.

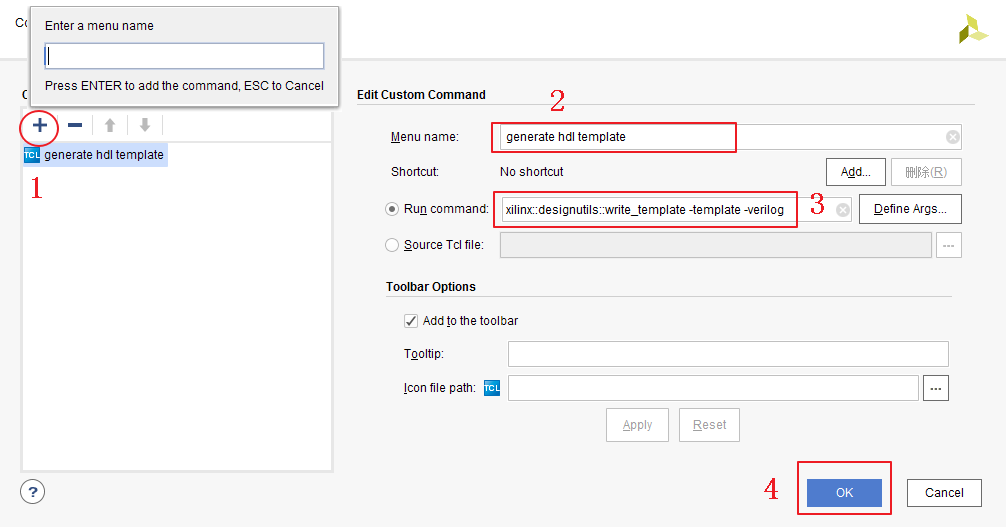

进去之后,按照下图的操作步骤,生成tcl指令。

图 7.

操作完后,就可以在vivado的菜单栏中看到tcl的按钮标志,如下图8所示。

图 8.

以后在敲指令的步骤就可以替代为直接点击该按钮即可。

“Vivado怎么生成HDL例化模板”的内容就介绍到这里了,感谢大家的阅读。如果想了解更多行业相关的知识可以关注蜗牛博客网站,小编将为大家输出更多高质量的实用文章!

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:niceseo99@gmail.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。

评论