如何浅析UVM概念中的topdown phase

本篇文章给大家分享的是有关如何浅析UVM概念中的topdown phase,小编觉得挺实用的,因此分享给大家学习,希望大家阅读完这篇文章后可以有所收获,话不多说,跟着小编一起来看看吧。

在学习UVM的phase机制时,我们知道build phase和final phase是topdown phase( function phase)

其他的phase都是bottomup phase(function phase ),或者task phase。

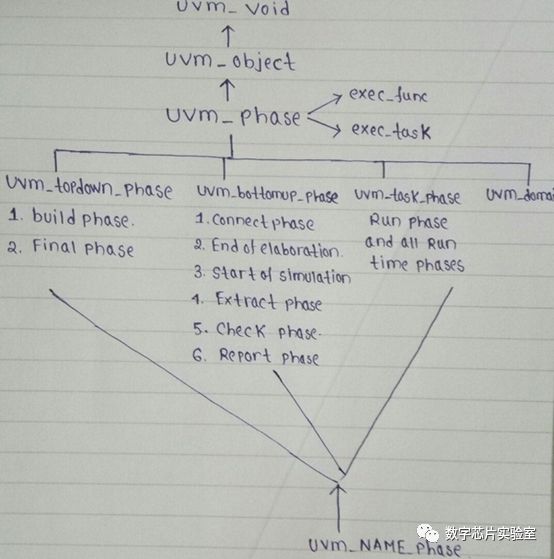

首先让我们看一下uvm phase机制的层次结构。

从上图可以看出,完整的phase机制分为三种类型的phase:

uvm_topdown_phase

uvm_bottomup_phase

uvm_task_phase

所有这些phase的类定义如下:

virtual class uvm_topdown_phase extends uvm_phaseclass uvm_build_phase extends uvm_topdown_phase

类似的,对于uvm_bottomup_phase

virtual class uvm_bottomup_phase extends uvm_phase

所以,为什么build phase和final phase是top down呢?

通常,当我们构建uvm 测试平台时,如果我们查看层次结构,我们会在顶层发现uvm_top,它是测试平台的静态组件。

如以下代码段所示:

module uvm_top();//DUTInstance//InterfaceInstance//Clockgenerationinitialbegin //VirtualInterface Instance ....... ....... run_test();endendmodule

因此,当从顶层调用run_test时,它将启动uvm phase机制,依次执行testbench的 testclass 、environment class、agent class的build phase.

final phase也是topdown phase。其余的function phase是bottomup phase,例如connect phase,其用于组件之间的TLM互连,并且通常需要向上移动层次结构。

以上就是如何浅析UVM概念中的topdown phase,小编相信有部分知识点可能是我们日常工作会见到或用到的。希望你能通过这篇文章学到更多知识。更多详情敬请关注蜗牛博客行业资讯频道。

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:niceseo99@gmail.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。

评论